임성갑 KAIST 생명화학공학과 교수와 김재준 POSTECH 창의IT융합공학과 교수 공동연구팀이 비아홀(via-hole) 공정 없이도 금속을 다중으로 상호 연결할 수 있는 기술을 개발했다고 밝혔습니다. 연구팀은 이를 통해 5층 이상의 3차원 고성능 유기 집적회로를 구현했다고 전했는데요.

이번 기술은 금속의 수직 상호 연결을 위해 공간을 뚫는 작업인 비아홀 공정 대신 패턴된 절연막을 직접 쌓는 방식으로 유기 반도체 집적회로를 형성하는 데 적용할 수 있는 신개념 공정입니다. 유기 트랜지스터는 구부리거나 접어도 그 특성을 그대로 유지할 수 있는 장점 덕분에 유연(flexible) 디스플레이 및 웨어러블 센서 등 다양한 분야에 적용할 수 있습니다.

그러나 이러한 유기물 반도체는 화학적 용매, 플라즈마, 고온 등에 의해 쉽게 손상되는 문제점 때문에 일반적인 식각 공정을 적용할 수 없어 유기 트랜지스터 기반 집적회로 구현의 걸림돌로 여겨졌는데요.

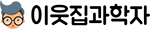

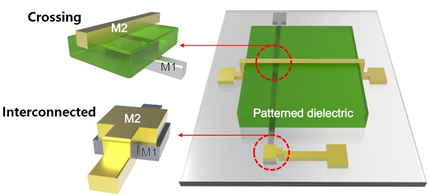

공동연구팀은 유기물 반도체의 손상 없이 안정적인 금속 전극 접속을 위해 절연막에 비아홀을 뚫는 기존 방식에서 벗어나 패턴된 절연막을 직접 쌓는 방식을 택했습니다. 패턴된 절연막은 패턴 구조에 따라 반도체소자를 선택적으로 연결할 수 있도록 했습니다. 특히 연구팀은 '개시제를 이용한 화학 기상 증착법(iCVD: initiated chemical vapor deposition)'을 통해 얇고 균일한 절연막 패턴을 활용해 안정적인 트랜지스터 및 집적회로를 구현하는 데 성공했습니다.

공동 연구팀은 긴밀한 협력을 통해 개발한 금속 상호 연결 방법이 유기물 손상 없이 100%에 가까운 소자 수율로 유기 트랜지스터를 제작할 수 있음을 확인했다고 해요. 제작된 트랜지스터는 탁월한 소자 신뢰성 및 균일성을 보여 유기 집적회로 제작에 큰 역할을 했습니다.

연구팀은 수직적으로 분포된 트랜지스터들을 상호 연결해 인버터, 낸드, 노어 등 다양한 디지털 논리 회로를 구현하는 데 성공했습니다. 또 효과적인 금속 상호 연결을 위한 레이아웃 디자인 규칙을 제안했는데요. 해당 성과는 향후 유기 반도체 기반 집적회로 구현 연구에 유용한 지침이 될 것으로 기대된다는 설명입니다.

김재준 POSTECH 교수는 "패턴된 절연막을 이용하는 발상의 전환이 유기 집적회로로 가기 위한 핵심 기술의 원천이 됐다"며 "향후 유기 반도체뿐 아니라 다양한 반도체 집적회로 구현의 핵심적인 역할을 할 것으로 기대한다"고 말했습니다. 이번 연구 결과는 국제학술지 <Nature Communications>에 게재됐습니다.